Elektroniczny układ scalony Obsługa BOM Usługa TPS54560BDDAR zupełnie nowe komponenty elektroniczne układów scalonych

Cechy produktu

| TYP | OPIS |

| Kategoria | Układy scalone (IC) |

| Mfr | Instrumenty Teksasu |

| Seria | Tryb Eco™ |

| Pakiet | Taśma i szpula (TR) Taśma cięta (CT) Digi-Reel® |

| SPQ | 2500T&R |

| Stan produktu | Aktywny |

| Funkcjonować | Spadek |

| Konfiguracja wyjściowa | Pozytywny |

| Topologia | Buck, dzielona szyna |

| Typ wyjścia | Nastawny |

| Liczba wyjść | 1 |

| Napięcie — wejście (min) | 4,5 V |

| Napięcie — wejście (maks.) | 60 V |

| Napięcie — moc wyjściowa (min./stała) | 0,8 V |

| Napięcie — wyjście (maks.) | 58,8 V |

| Prąd - Wyjście | 5A |

| Częstotliwość - przełączanie | 500 kHz |

| Prostownik synchroniczny | No |

| temperatura robocza | -40°C ~ 150°C (TJ) |

| Typ mocowania | Montaż powierzchniowy |

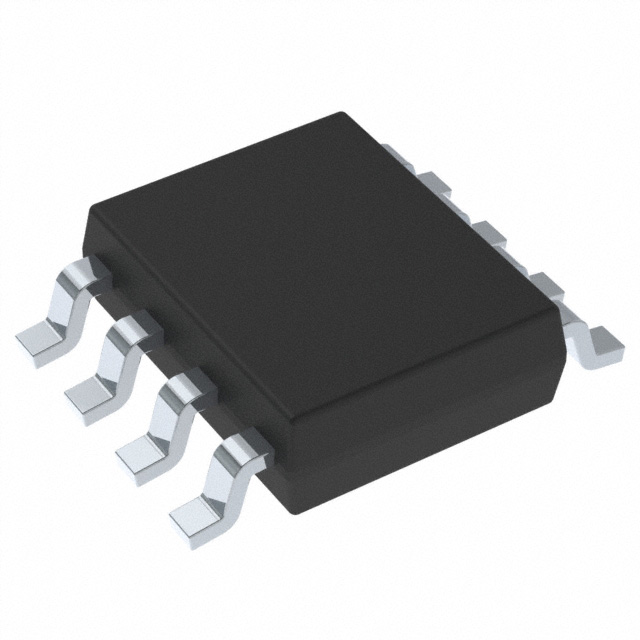

| Opakowanie/etui | 8-PowerSOIC (szerokość 0,154 cala, 3,90 mm) |

| Pakiet urządzeń dostawcy | PowerPad 8-SO |

| Podstawowy numer produktu | TPS54560 |

1.Nazewnictwo układów scalonych, ogólna wiedza o pakietach i zasady nazewnictwa:

Zakres temperatury.

C=0°C do 60°C (klasa handlowa);I=-20°C do 85°C (klasa przemysłowa);E=-40°C do 85°C (rozszerzona klasa przemysłowa);A= -40°C do 82°C (klasa lotnicza);M=-55°C do 125°C (klasa wojskowa)

Typ przesyłki.

A-SSOP;B-CERQUAD;C-TO-200, TQFP;Miedziany blat D-Ceramic;E-QSOP;F-Ceramika SOP;H-SBGAJ – ceramiczny DIP;K-TO-3;L-LCC, M-MQFP;N-wąski DIP;N-DIP;Q PLCC;R - Wąski ceramiczny DIP (300mil);S - TO-52, T - TO5, TO-99, TO-100;U - TSSOP, uMAX, SOT;W - Wide Small Form Factor (300 mil) W - Wide Small Form Factor (300 mil);X-SC-60 (3P, 5P, 6P);Y-Wąski miedziany blat;Z-TO-92, MQUAD;D-umrzeć;/PR-Tworzywo sztuczne wzmocnione;/W-Wafer.

Liczba pinów:

a-8;b-10;c-12, 192;d-14;e-16;f-22, 256;g-4;h-4;i -4;H-4;I-28;J-2;K-5, 68;L-40;M-6, 48;N 18;O-42;P-20;Q-2, 100;R-3, 843;S-4, 80;T-6, 160;U-60 -6160;U-60;V-8 (okrągły);W-10 (okrągły);X-36;Y-8 (okrągły);Z-10 (okrągły).(okrągły).

Uwaga: Pierwsza litera czteroliterowego przyrostka klasy interfejsu to E, co oznacza, że urządzenie posiada funkcję antystatyczną.

2.Rozwój technologii pakowania

W najwcześniejszych układach scalonych zastosowano płaskie obudowy ceramiczne, które przez wiele lat były używane w wojsku ze względu na ich niezawodność i niewielkie rozmiary.Komercyjne opakowania obwodów wkrótce przeszły na opakowania z podwójnymi liniami, zaczynając od ceramiki, a następnie z tworzywa sztucznego, a w latach 80. liczba pinów obwodów VLSI przekroczyła granice zastosowań pakietów DIP, co ostatecznie doprowadziło do pojawienia się układów siatki pinów i nośników chipów.

Pakiet do montażu powierzchniowego pojawił się na początku lat 80. XX wieku i stał się popularny w dalszej części tej dekady.Wykorzystuje mniejszą podziałkę szpilek i ma kształt szpilki w kształcie skrzydła mewy lub litery J.Na przykład układ scalony o małym zarysie (SOIC) ma o 30–50% mniejszą powierzchnię i jest o 70% mniej gruby niż równoważny układ DIP.To opakowanie ma szpilki w kształcie skrzydeł mewy wystające z dwóch długich boków i rozstaw szpilek 0,05 cala.

Pakiety układów scalonych o małym zarysie (SOIC) i PLCC.XX wieku, chociaż pakiet PGA był nadal często używany w mikroprocesorach z najwyższej półki.PQFP i pakiet cienkich małych konturów (TSOP) stały się zwykłym pakietem dla urządzeń o dużej liczbie pinów.Wysokiej klasy mikroprocesory Intel i AMD przeszły z pakietów PGA (Pine Grid Array) na pakiety Land Grid Array (LGA).

Pakiety Ball Grid Array zaczęły pojawiać się w latach 70. XX wieku, a w latach 90. opracowano pakiet FCBGA z większą liczbą pinów niż inne pakiety.W pakiecie FCBGA matryca jest odwracana w górę i w dół i połączona z kulkami lutowniczymi na opakowaniu za pomocą warstwy podstawowej przypominającej płytkę PCB, a nie przewodów.Na dzisiejszym rynku opakowanie również stanowi odrębną część procesu, a technologia opakowania może również wpływać na jakość i wydajność produktu.