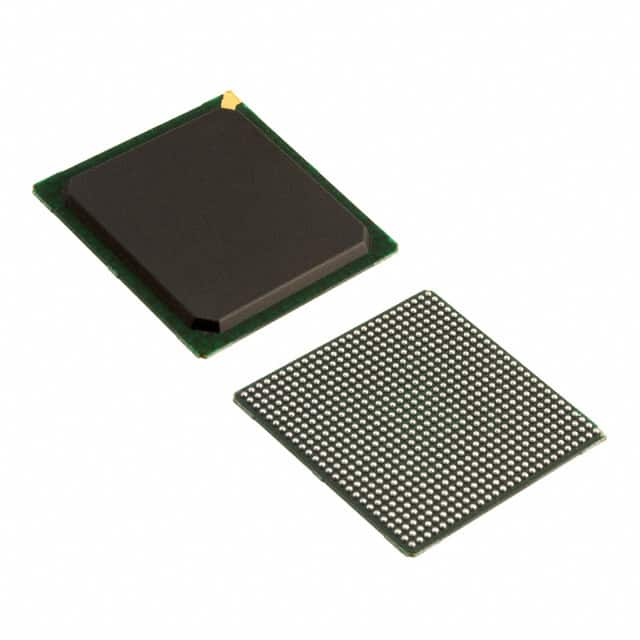

Deserializator LVDS 2975 Mb/s 0,6 V Motoryzacyjny 48-pinowy WQFN EP T/R DS90UB928QSQX/NOPB

Cechy produktu

| TYP | OPIS |

| Kategoria | Układy scalone (IC) |

| Mfr | Instrumenty Teksasu |

| Seria | Motoryzacja, AEC-Q100 |

| Pakiet | Taśma i szpula (TR) Taśma cięta (CT) Digi-Reel® |

| SPQ | 2500T&R |

| Stan produktu | Aktywny |

| Funkcjonować | Deserializator |

| Prędkość transmisji danych | 2,975 Gb/s |

| Typ wejścia | FPD-Link III, LVDS |

| Typ wyjścia | LVDS |

| Liczba wejść | 1 |

| Liczba wyjść | 13 |

| Napięcie zasilające | 3 V ~ 3,6 V |

| temperatura robocza | -40°C ~ 105°C (TA) |

| Typ mocowania | Montaż powierzchniowy |

| Opakowanie/etui | 48-WFQFN Odsłonięta podkładka |

| Pakiet urządzeń dostawcy | 48-WQFN (7x7) |

| Podstawowy numer produktu | DS90UB928 |

1. Obwody scalone wykonane na powierzchni chipa półprzewodnikowego są również znane jako cienkowarstwowe układy scalone.Innym typem grubowarstwowego układu scalonego (hybrydowy układ scalony) jest zminiaturyzowany obwód składający się z pojedynczych elementów półprzewodnikowych i elementów pasywnych zintegrowanych z podłożem lub płytką drukowaną.

W latach 1949-1957 prototypy opracowywali Werner Jacobi, Jeffrey Dummer, Sidney Darlington i Yasuo Tarui, ale nowoczesny układ scalony został wynaleziony przez Jacka Kilby'ego w 1958 roku.W 2000 roku otrzymał za to Nagrodę Nobla w dziedzinie fizyki, ale Robert Noyce, który w tym samym czasie opracował nowoczesny, praktyczny układ scalony, zmarł w 1990 roku.

Po wynalezieniu i masowej produkcji tranzystora, w dużych ilościach zastosowano różne półprzewodnikowe elementy półprzewodnikowe, takie jak diody i tranzystory, zastępując funkcję i rolę lampy próżniowej w obwodzie.Od połowy do końca XX wieku postęp w technologii produkcji półprzewodników umożliwił powstanie układów scalonych.W przeciwieństwie do ręcznego składania obwodów z wykorzystaniem pojedynczych dyskretnych elementów elektronicznych, układy scalone pozwoliły na zintegrowanie dużej liczby mikrotranzystorów w mały chip, co było ogromnym postępem.Skalowalna produktywność, niezawodność i modułowe podejście do projektowania obwodów układów scalonych zapewniły szybkie przyjęcie standardowych układów scalonych zamiast projektowania przy użyciu dyskretnych tranzystorów.

2. Obwody scalone mają dwie główne zalety w porównaniu z tranzystorami dyskretnymi: koszt i wydajność.Niski koszt wynika z tego, że chipy drukują wszystkie komponenty jako całość za pomocą fotolitografii, zamiast tworzyć tylko jeden tranzystor na raz.Wysoka wydajność wynika z szybkiego przełączania komponentów i zużywania mniejszej ilości energii, ponieważ komponenty są małe i blisko siebie.W roku 2006 uzyskano obszary chipów o powierzchni od kilku milimetrów kwadratowych do 350 mm² i do miliona tranzystorów na mm².

Prototypowy układ scalony został ukończony przez Jacka Kilby'ego w 1958 roku i składał się z tranzystora bipolarnego, trzech rezystorów i kondensatora.

W zależności od liczby urządzeń mikroelektronicznych zintegrowanych w chipie, układy scalone można podzielić na następujące kategorie.

Małe układy scalone (SSI) mają mniej niż 10 bramek logicznych lub 100 tranzystorów.

Integracja średniej skali (MSI) obejmuje od 11 do 100 bramek logicznych lub od 101 do 1 tys. tranzystorów.

Integracja wielkoskalowa (LSI) od 101 do 1 tys. bramek logicznych lub od 1001 do 10 tys. tranzystorów.

Integracja na bardzo dużą skalę (VLSI) 1001–10 tys. bramek logicznych lub 10 001–100 tys. tranzystorów.

Integracja na dużą skalę (ULSI) 10 001 ~ 1 M bramek logicznych lub 100 001 ~ 10 M tranzystorów.

GLSI (Giga Scale Integration) 1 000 001 lub więcej bramek logicznych lub 10 000 001 lub więcej tranzystorów.

3.Rozwój układów scalonych

Najbardziej zaawansowane układy scalone stanowią serce mikroprocesorów lub procesorów wielordzeniowych, które mogą sterować wszystkim, od komputerów po telefony komórkowe i cyfrowe kuchenki mikrofalowe.Choć koszt zaprojektowania i opracowania złożonego układu scalonego jest bardzo wysoki, koszt przypadający na jeden układ scalony jest minimalizowany w przypadku rozłożenia go na produkty, które często liczone są w milionach.Wydajność układów scalonych jest wysoka, ponieważ mały rozmiar skutkuje krótkimi ścieżkami, umożliwiając stosowanie obwodów logicznych o małej mocy przy dużych prędkościach przełączania.

Przez lata nadal zmierzałem w kierunku mniejszych obudów, umożliwiając pakowanie większej liczby obwodów w jednym chipie.Zwiększa to pojemność na jednostkę powierzchni, pozwalając na niższe koszty i zwiększoną funkcjonalność, patrz prawo Moore'a, gdzie liczba tranzystorów w układzie scalonym podwaja się co 1,5 roku.Podsumowując, prawie wszystkie wskaźniki poprawiają się wraz ze zmniejszaniem się współczynników kształtu, spadkiem kosztów jednostkowych i zużycia energii przełączania oraz wzrostem prędkości.Istnieją jednak również problemy z układami scalonymi, które integrują urządzenia w skali nano, głównie z prądami upływowymi.W rezultacie wzrost prędkości i zużycia energii jest bardzo zauważalny dla użytkownika końcowego, a producenci stają przed ostrym wyzwaniem zastosowania lepszej geometrii.Proces ten i oczekiwany postęp w nadchodzących latach dobrze opisuje międzynarodowy plan rozwoju technologii półprzewodników.

Zaledwie pół wieku po ich opracowaniu układy scalone stały się wszechobecne, a komputery, telefony komórkowe i inne urządzenia cyfrowe stały się integralną częścią tkanki społecznej.Dzieje się tak dlatego, że nowoczesne systemy komputerowe, komunikacyjne, produkcyjne i transportowe, w tym Internet, zależą od istnienia układów scalonych.Wielu uczonych uważa nawet rewolucję cyfrową wywołaną przez układ scalony za najważniejsze wydarzenie w historii ludzkości i że dojrzewanie układu scalonego doprowadzi do wielkiego postępu technologicznego, zarówno pod względem technik projektowania, jak i przełomów w procesach półprzewodnikowych , oba są ze sobą ściśle powiązane.