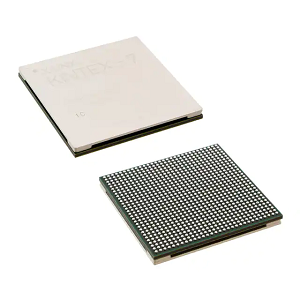

XC7K420T-2FFG901I – Układy scalone, wbudowane, programowalne macierze bramek

Cechy produktu

| TYP | ZILUSTROWAĆ |

| Kategoria | Układy scalone (IC)Osadzony Programowalne macierze bramek (FPGA) |

| producent | AMD |

| seria | Kintex®-7 |

| zawinąć | taca |

| Stan produktu | Aktywny |

| DigiKey jest programowalny | Nie zweryfikowany |

| Numer LAB/CLB | 32575 |

| Liczba elementów/jednostek logicznych | 416960 |

| Całkowita liczba bitów RAM | 30781440 |

| Liczba wejść/wyjść | 380 |

| Napięcie - Zasilanie | 0,97 V ~ 1,03 V |

| Typ instalacji | Typ kleju powierzchniowego |

| Temperatura robocza | -40°C ~ 100°C (TJ) |

| Opakowanie/Obudowa | 900-BBGA, FCBGA |

| Hermetyzacja komponentów dostawcy | 901-FCBGA (31x31) |

| Numer główny produktu | XC7K420 |

| TYP | ZILUSTROWAĆ |

| Kategoria | Układy scalone (IC)Osadzony |

| producent | AMD |

| seria | Kintex®-7 |

| zawinąć | taca |

| Stan produktu | Aktywny |

| DigiKey jest programowalny | Nie zweryfikowany |

| Numer LAB/CLB | 32575 |

| Liczba elementów/jednostek logicznych | 416960 |

| Całkowita liczba bitów RAM | 30781440 |

| Liczba wejść/wyjść | 380 |

| Napięcie - Zasilanie | 0,97 V ~ 1,03 V |

| Typ instalacji | Typ kleju powierzchniowego |

| Temperatura robocza | -40°C ~ 100°C (TJ) |

| Opakowanie/Obudowa | 900-BBGA, FCBGA |

| Hermetyzacja komponentów dostawcy | 901-FCBGA (31x31) |

| Numer główny produktu | XC7K420 |

Układy FPGA

Zalety

Zalety układów FPGA są następujące:

(1) Układy FPGA składają się z zasobów sprzętowych, takich jak komórki logiczne, pamięć RAM, mnożniki itp. Dzięki racjonalnej organizacji tych zasobów sprzętowych można wdrożyć obwody sprzętowe, takie jak mnożniki, rejestry, generatory adresów itp.

(2) Układy FPGA można projektować przy użyciu schematów blokowych lub Verilog HDL, od prostych obwodów bramkowych po obwody FIR lub FFT.

(3) Układy FPGA można bez końca przeprogramowywać, ładując nowe rozwiązanie projektowe w zaledwie kilkaset milisekund, korzystając z rekonfiguracji w celu zmniejszenia obciążenia sprzętowego.

(4) Częstotliwość robocza układu FPGA jest określona przez układ FPGA oraz konstrukcję i może zostać zmodyfikowana lub zastąpiona szybszym układem, aby spełnić określone wymagania (choć oczywiście częstotliwość robocza nie jest nieograniczona i może zostać zwiększona, ale jest regulowane przez obecne procesy IC i inne czynniki).

Niedogodności

Wady układów FPGA są następujące:

(1) Układy FPGA opierają się na implementacji sprzętowej wszystkich funkcji i nie mogą realizować operacji takich jak rozgałęziające skoki warunkowe.

(2) Układy FPGA mogą realizować tylko operacje stałoprzecinkowe.

Podsumowując: układy FPGA wykorzystują sprzęt do realizacji wszystkich funkcji i można je porównać do dedykowanych układów pod względem szybkości, ale istnieje duża luka w elastyczności projektowania w porównaniu z procesorami ogólnego przeznaczenia.

Języki i platformy projektowania

Programowalne urządzenia logiczne to nośniki sprzętu, które konkretyzują ustalone funkcje i specyfikacje techniczne aplikacji elektronicznych za pośrednictwem technologii EDA.Układy FPGA, jako jedno z głównych urządzeń realizujących tę ścieżkę, są bezpośrednio zorientowane na użytkownika, niezwykle elastyczne i wszechstronne, łatwe w użyciu oraz szybkie w testowaniu i wdrażaniu sprzętowym.

Język opisu sprzętu (HDL) to język używany do projektowania cyfrowych systemów logicznych i opisywania obwodów cyfrowych, a głównymi powszechnie używanymi są VHDL, Verilog HDL, System Verilog i System C.

Jako wszechstronny język opisu sprzętu, bardzo szybki język opisu sprzętu układu scalonego (VHDL) charakteryzuje się niezależnością od konkretnego obwodu sprzętowego i platformą projektową, z zaletami możliwości opisu o szerokim zakresie, a nie zależny od konkretnych urządzeń oraz możliwość opisania projektu złożonej logiki sterującej w rygorystycznym i zwięzłym kodzie itp. Jest wspierany przez wiele firm EDA i jest szeroko stosowany w dziedzinie projektowania elektroniki.popularne.

VHDL jest językiem wysokiego poziomu do projektowania obwodów i w porównaniu z innymi językami opisu sprzętu charakteryzuje się prostym językiem, elastycznością i niezależnością od projektu urządzenia, co czyni go powszechnym językiem opisu sprzętu dla technologii EDA i czyni technologię EDA bardziej dostępne dla projektantów.

Verilog HDL to szeroko stosowany język opisu sprzętu, którego można używać na wielu etapach procesu projektowania sprzętu, w tym w modelowaniu, syntezie i symulacji.

Zalety Verilog HDL: podobny do C, łatwy do nauczenia i elastyczny.Wielkość liter ma znaczenie.Zalety pisania bodźców i modelowania.Wady: wielu błędów nie można wykryć w czasie kompilacji.

Zalety VHDL: rygorystyczna składnia, przejrzysta hierarchia.Wady: długi czas przyzwyczajenia, niewystarczająco elastyczny.

Oprogramowanie Quartus_II to kompletne, wieloplatformowe środowisko projektowe opracowane przez firmę Altera, które może spełniać potrzeby projektowe różnych układów FPGA i CPLD, a także stanowi kompleksowe środowisko do projektowania programowalnych systemów na chipie.

Vivado Design Suite, zintegrowane środowisko projektowe wydane przez dostawcę układów FPGA, firmę Xilinx, w 2012 roku. Zawiera wysoce zintegrowane środowisko projektowe i narzędzia nowej generacji, od poziomu systemu po układ scalony, a wszystko to zbudowane w oparciu o współdzielony, skalowalny model danych i wspólne środowisko debugowania.pakiet Xilinx Vivado Design Suite zapewnia rdzenie IP FIFO, które można łatwo zastosować w projektach.