XCVU9P-2FLGB2104I FPGA,VIRTEX ULTRASCALE,FCBGA-2104

Informacje o produkcie

| TYPNr.bloków logicznych: | 2586150 |

| Liczba makrokomórek: | 2586150Makrokomórki |

| Rodzina FPGA: | Seria Virtex UltraScale |

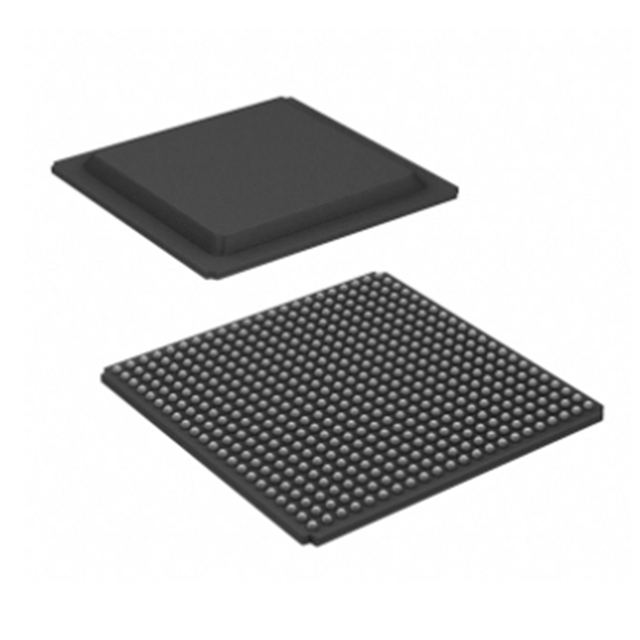

| Styl obudowy logicznej: | FCBGA |

| Liczba pinów: | 2104Piny |

| Liczba stopni prędkości: | 2 |

| Całkowita liczba bitów RAM: | 77722 Kbit |

| Liczba wejść/wyjść: | 778 wejść/wyjść |

| Zarządzanie zegarem: | MMCM, PLL |

| Min. napięcie zasilania rdzenia: | 922mV |

| Maks. napięcie zasilania rdzenia: | 979 mV |

| Napięcie zasilania we/wy: | 3,3 V |

| Częstotliwość robocza maks.: | 725 MHz |

| Zakres produktów: | Virtex UltraScale XCVU9P |

| MSL: | - |

Wprowadzenie produktów

BGA oznaczaPakiet Ball Grid Q Array.

Pamięć zamknięta w technologii BGA może zwiększyć pojemność pamięci nawet trzykrotnie bez zmiany objętości pamięci, BGA i TSOP

W porównaniu z ma mniejszą objętość, lepszą wydajność rozpraszania ciepła i wydajność elektryczną.Technologia pakowania BGA znacznie poprawiła pojemność pamięci na cal kwadratowy, wykorzystując produkty pamięci w technologii pakowania BGA o tej samej pojemności, objętość wynosi tylko jedną trzecią opakowania TSOP;Na dodatek z tradycją

W porównaniu z pakietem TSOP, pakiet BGA ma szybszy i bardziej efektywny sposób odprowadzania ciepła.

Wraz z rozwojem technologii układów scalonych wymagania dotyczące pakowania układów scalonych są coraz bardziej rygorystyczne.Dzieje się tak dlatego, że technologia pakowania jest powiązana z funkcjonalnością produktu, gdy częstotliwość układu scalonego przekracza 100 MHz, tradycyjna metoda pakowania może powodować tzw. zjawisko „przesłuchu”, a liczba pinów układu scalonego jest większa niż 208 pinów, tradycyjna metoda pakowania wiąże się z pewnymi trudnościami. Dlatego też oprócz stosowania opakowań QFP większość współczesnych układów o dużej liczbie pinów (takich jak układy graficzne i chipsety itp.) jest przełączana na BGA (Ball Grid Array Technologia pakowania PackageQ). Kiedy pojawiło się BGA, stało się najlepszym wyborem dla wielopinowych pakietów o dużej gęstości i wydajności, takich jak procesory i układy mostka południowego/północnego na płytach głównych.

Technologię pakowania BGA można również podzielić na pięć kategorii:

1. Podłoże PBGA (plastikowe BGA): Zwykle 2-4 warstwy materiału organicznego składającego się z płyty wielowarstwowej.Procesor z serii Intel, Pentium 1l

Wszystkie procesory Chuan IV są pakowane w tej formie.

2. Podłoże CBGA (CeramicBCA): czyli podłoże ceramiczne, połączenie elektryczne między chipem a podłożem jest zwykle typu flip-chip

Jak zainstalować FlipChip (w skrócie FC).Wykorzystywane są procesory z serii Intel, Pentium l, ll Pentium Pro

Forma enkapsulacji.

3.FCBGAPodłoże (FilpChipBGA): Twarde podłoże wielowarstwowe.

4. Podłoże TBGA (TapeBGA): Podłoże to miękka, 1-2-warstwowa płytka drukowana wstęgowa.

5. Podłoże CDPBGA (Carty Down PBGA): odnosi się do małego kwadratowego obszaru chipa (znanego również jako obszar wnęki) w środku opakowania.

Pakiet BGA ma następujące funkcje:

1).10 Zwiększono liczbę szpilek, ale odległość między szpilkami jest znacznie większa niż w przypadku opakowania QFP, co poprawia wydajność.

2). Chociaż zużycie energii przez układ BGA jest zwiększone, wydajność ogrzewania elektrycznego można poprawić dzięki metodzie kontrolowanego zgrzewania wiórów.

3).Opóźnienie transmisji sygnału jest niewielkie, a częstotliwość adaptacyjna znacznie się poprawia.

4).Montaż może być spawany współpłaszczyznowo, co znacznie poprawia niezawodność.